米半導体大手のマイクロンテクノロジーが発表した2021年度第1四半期(20年9~11月)業績は、売上高が57.7億ドル(前四半期比5%減/前年同期比12%増)、営業利益が9.7億ドル(同25%減/同64%増)となり、前四半期比で減収減益となったものの、12月初旬に発表していた修正ガイダンスも上回る結果となった。

12月初旬に修正予想発表

前回決算発表時点で、第1四半期の売上高予想を50億~54億ドルと見込んでいた。中国ファーウェイへの制裁強化に伴い、モバイル向けを中心に需要低下を想定していたが、その後、他のスマートフォン顧客からの引き合い増加を受けて、12月1日に業績の修正予想を発表。売上高を57億~57.5億ドルと計画していたが、結果はこれもわずかに上回るものとなった。

売上高の70%を占めたDRAMは、ビット出荷が前四半期比で1桁台前半の減少、ASP(平均売価)も1桁台半ばの下落となり、売上高は41億ドル(同7%減/同17%増)。NANDはビット出荷が10%台後半の増加を見せたものの、ASPが10%台前半の下落となり、売上高は16億ドル(同3%増/同11%増)となった。

第2四半期の業績見通しについて、売上高は56億~60億ドルを見込んでおり、ミッドポイントは前四半期比横ばいを想定する。メモリーの市場見通しについて、DRAMのビット需要は20年が前年比20%強、21年が10%台後半の成長を予想。NANDビット需要は20年が20%台半ば、21年が約30%の成長を見込んでおり、DRAMは需要に対して供給が下回ると予想する一方、NANDは供給過多が続くことを示唆した。ただし、需要の価格弾力性が働くことで需給は改善方向に向かうとしている。

台湾地区で停電・地震被害

台湾地区にあるDRAM工場の操業については、20年12月3日に桃園工場で停電被害があったほか、12月10日には桃園ならびに台中工場で地震の影響を受けた。同社によれば、ここ数年のクリーンルーム管理への継続的な投資により、影響は最小限に食い止めることができているとしているものの、第2四半期業績予想にこれら影響が織り込まれていると説明した。

R&D体制を一層強化

同社はR&D体制の強化にも一層力を入れている。これまで開きがあった競合他社との技術ギャップを埋めることができたとしており、今後は最先端技術を積極的に取り入れて業界をリードしていく姿勢を強調した。DRAMの微細化においては、向こう2世代も既存のArF液浸露光技術を延命させる方針で、競合する韓国勢とは異なる技術ロードマップを示している。

同社は16~20年までの5カ年について、競合他社との技術格差を埋める期間だったと位置づけており、微細化のほか、高付加価値市場へのシフトを進めてきた。NAND事業においては約8割(ビット基準)がSSDをはじめとする高付加価値市場で構成されるようになってきており、製品ミックスも良化している。

21年以降、同社では技術・製品の双方でリーダーシップを発揮していきたい考えで、業界トップの最先端技術を積極的に取り入れていく。R&D効率の向上のため、組織体制の見直しにも着手。これにより、顧客ニーズをR&Dにうまく反映できるようになってきたとしている。

DRAMは液浸延命

DRAM分野では1α世代の量産を21年上期から開始する。1αは1Zに比べてウエハーあたりのビット容量を4割高めるなど高密度化を実現。消費電力も15%低減している。1αもArF液浸のマルチプルパターニングで対応するほか、1β、1γの世代についてもEUVは導入せず液浸露光が主体となる見込み。

コスト面でArF液浸の方が有利であるとしており、この傾向は今後数年間変わらないとしている。1γの次の世代にあたる1δで初めてEUVの導入について検討を行っていく。

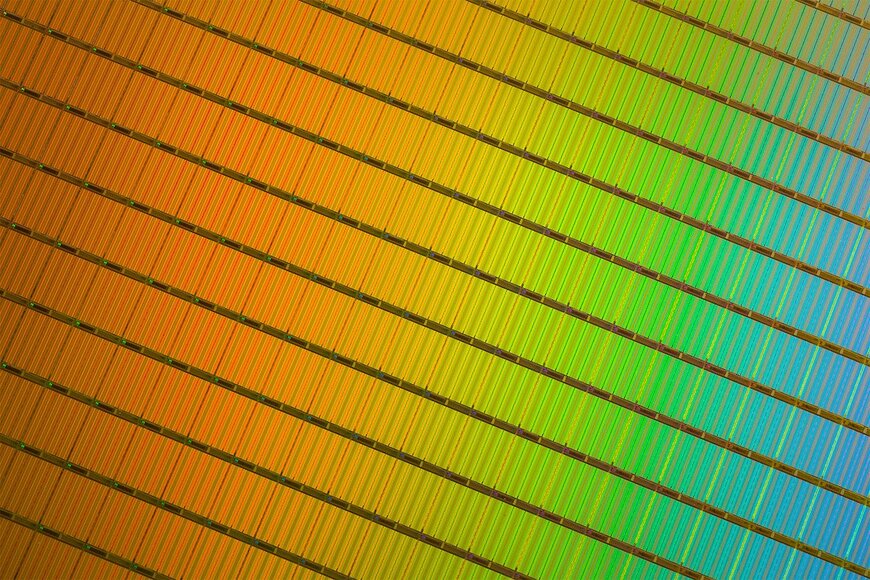

176層品を発表、CUAで競争力協調

NANDについては、20年11月に176層の3D-NANDを発表。ロジック部をメモリーセル直下に配置することで、ダイ面積を競合製品に比べて3割縮小、高いコスト競争力を発揮するという。3D-NANDの主力工場であるシンガポール工場で量産を開始、TLC(Triple Level Cell)ベースの512Gb(Gビット)品の出荷を一部開始しており、21年中ごろをめどにQLC(Quad Level Cell)品の出荷も開始する。

同社は04年にNAND分野に参入。15年から3D-NANDも手がけており、今回の176層品は3D-NANDとしては第5世代目、RG(Replacement Gate)方式として第2世代目にあたる。同社はこれまで、FG(Floating Gate)方式による3D-NANDを開発・量産してきたが、128層世代以降は、シリコン層の代わりに伝導性の高い金属ワード線を用いるRG技術と、CT(Charge Trap)技術を組み合わせた世代に移行している。

今回発表した176層には88+88層のスタックプロセス。前世代と比較して読み書きのレイテンシーが35%以上改善されているほか、ロジック部をメモリーセル直下に集積化するCUA(CMOS Under Array)技術を取り入れることで、競合製品と比べて3割の面積縮小を図れているという。

電子デバイス産業新聞 副編集長 稲葉 雅巳