㈱ピーエムティー(PMT、福岡県糟屋郡須恵町)は、ハーフインチ(0.5インチ)ウエハーを用いるミニマルファブを活用したFOWLP(Fan-Out Wafer Level Package)の試作サービスを本格化している。2019年2月の開始以降、すでに複数の受注実績を上げており、数チップから手軽に試作してFOWLPの性能を試すことが可能だ。

ミニマルファブって何?

ミニマルファブとは、0.5インチのシリコンウエハーを用い、幅30cmのウォーターサーバーくらいのサイズのミニマル製造装置群を多数並べて、究極の少量多品種生産を実現してしまおうという、全く新しい半導体生産システムである。これにより、300mmウエハーを用いた最新鋭工場を建設するなら数千億円が必要になる設備投資額を1/1000に抑え、わずか5億円で超コンパクトな半導体製造ラインを構築するという取り組みだ。

産業技術総合研究所が中心となり、半導体関連メーカー100社以上が集結し、それぞれに工程を分担しながらミニマル生産システムの開発に取り組んでいる。この生産システムは大量生産には向かないが、従来なら多大な製造コストがかかる半導体を少量かつ低コストで生産できると期待されている。PMTは、このミニマルファブプロジェクトでマスクレス露光装置の開発を担当している。

すでに複数の試作実績あり

PMTのFOWLP試作サービスでは、このマスクレス露光装置に自社開発の周辺装置、一部外注を組み合わせ、試作に必要なチップファースト型プロセスを確立した。すでにセンサーやパワーデバイスのFOWLP、医療用のWLCSP(Wafer Level Chip Scale Package)、MEMSとLSIを組み合わせたマルチチップSiP(System in Package)センサーシステムなどの受注実績がある。

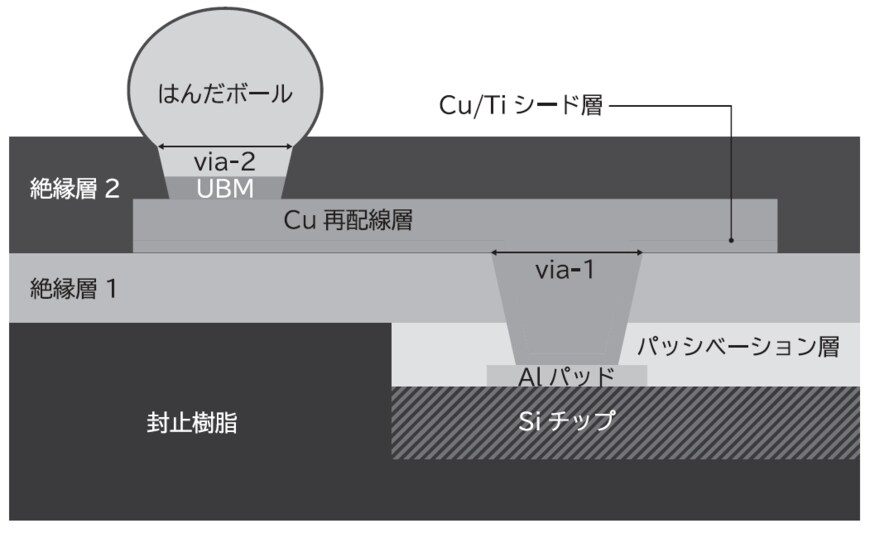

試作プロセスの流れは、まずキャリア基板となるハーフインチウエハーにフェースダウンでICを実装し、これをモールド樹脂封止する。搭載するICは顧客から提供を受ける。その後、キャリア基板を剥離してフェースアップ状態とし、マスクレス露光で一連の再配線工程を実施する。窓あけやアンダーバリアメタル(UBM)の無電解めっきを施し、はんだボールを搭載する。ボールではなく、AuパッドやCuパッドを形成することもできる。

主な仕様は、▽ビア径=最小20μm、▽ライン&スペース(L/S)=20/20μm(銅配線)、▽ボール径=150~500μm、▽ボールピッチ=300μm以上、▽再配線層の膜厚=3~10μm、▽再配線層の線幅=20μm。

搭載するチップは厚さ100~500μm、サイズ1~7.4mm角まで対応するが、現在は0.7mm

角まで対応できるようになっているという。

高いコストと長い納期を解消

FOWLPは、半導体パッケージ形態の1つ。半導体のチップ面積とパッケージの面積が同じであるWLCSPに対し、FOWLPはチップ面積よりパッケージ面積の方が大きいが、再配線工程によってチップの端子から外側に端子を引き出す(Fan-Out)ためパッケージ基板が不要で、薄く低コストな半導体パッケージができると期待されている。

このように小型化が可能なため、FOWLPのニーズ自体は高いが、現在はウエハーフォーマットまたはパネルフォーマット(FOPLP=Fan-Out Panel Level Package)であるため少量生産が難しく、試作には高いコストと長い納期を要するのが実情。性能が向上できると分かっていても、量産には採用しづらいのが実態である。

短納期で少量生産を受託可能

これに対し、PMTの試作サービスは、ハーフインチで数チップから試作が可能で、ハーフインチウエハー内に複数のICを搭載することもできる。低価格・短納期で少量生産できるのがメリットだ。

PMTミニマルファウンドリ推進室の三宅賢治氏は「コアファンアウトと呼ばれる小型パッケージの試作市場に特化して市場を開拓していきたい。80μm程度の薄いパッケージも作成可能で、チップ裏面を露出させたりして、放熱性を高めることも可能。フリップチップによるバンプ接続にも対応するなど、プロセスの自由度は高い」と話している。

電子デバイス産業新聞 編集長 津村 明宏