半導体パッケージ分野において、ファンアウトパッケージが注目されるようになって久しい。TSMCが開発した独自のファンアウト技術「InFO(Integrated Fan Out)」がアップルのiPhone用プロセッサーに採用されたことを契機に、市場が一気に活性化した。

問題はやはりコスト

ファンアウトは従来、パッケージ基板(サブストレート)を用いてパッケージングを行っていたものを、半導体プロセスを用いた再配線(RDL)層などに置き換えることで、パッケージの薄型化、電気特性・放熱性の向上、反りの低減などを図る「基板レス」のパッケージ技術だ。

InFO採用当時はアップルだけでなく、将来的にはクアルコムやメディアテックといった競合のモバイル用プロセッサーメーカーもファンアウトの採用に踏み切るとの見方もあったが、数年たった今、その答えは「ノー」だった。

問題はやはり、コストに起因する。モバイル用プロセッサーはスマートフォン(スマホ)に搭載するため、コスト意識が厳しい。特にクアルコムやメディアテックは中国スマホ市場を主戦場の1つと位置づけているため、コスト高となるファンアウトの採用に消極的であった。

こうした状況のなか、ファンアウトパッケージは今後、モバイル系プロセッサーではなく、サーバーやクラウド、通信ネットワークなど、よりハイエンド領域に用途が限られることになりそうだ。シリコンインターポーザーを使った2.5Dパッケージとともに、異種チップを同一パッケージ内で接合・接続するような形で、従来と方向性が大きく変わってくる見通しだ。

大判化でコストダウンに有利

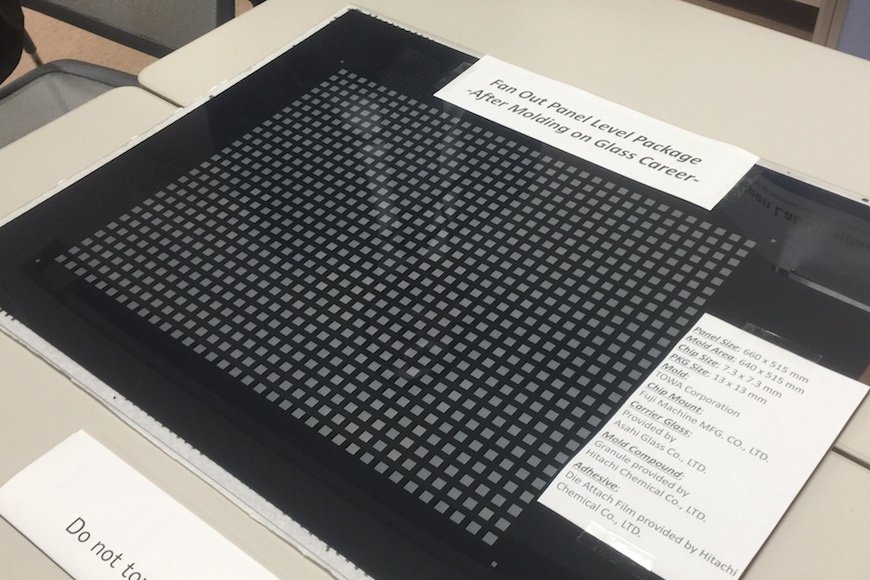

コストという大きな壁にぶつかるなか、従来工法と異なるアプローチで低コストを実現しようとする試みがある。それがパネルベースのファンアウト技術である「FOPLP(Fan Out Panel Level Package)」だ。

FOPLPとはInFOのようにウエハータイプの丸型基板(キャリア)を用いずに、角型基板を用いて、ファンアウト化させるパッケージ技術だ。通常、丸型基板ではあれば、300mmウエハーサイズが一般的であるが、角型基板では400×500mmのように大きなワークサイズを用いることができ、コストダウンが図りやすい。

よって、コストに厳しいスマホなどのコンシューマー分野でのファンアウト採用は将来的に、FOPLPがメジャーになる可能性が高いといえる。

サムスンがFOPLPの量産を開始

ファンアウトに関しては、以前からサムスン電子が積極的に開発を進めてきた。グループ企業のSEMCO(サムスン電機)と協業し、一部グループで遊休設備となっていた液晶ラインなどを活用。先ごろ、FOPLPを用いたモバイル用プロセッサーの量産を開始したとアナウンスした。

実際の製品はサムスンのウエアラブルウォッチである「Galaxy Gear S4」に搭載されているという。今後はPMIC(Power Management IC)などに適用するほか、将来的にはDRAMなどメモリー分野にも展開していきたい考えを持つ。

東芝やマイクロンテクノロジーなどを顧客に持つ台湾OSAT(Outsourced Semiconductor Assembly & Test=半導体後工程の受託専門企業)のパワーテック・テクノロジー(力成科技)も、9月にFOPLPの専門工場となる新棟建設を開始した。20年前半に工事が完了、20年後半からの量産開始を計画する。加えて、同じく台湾OSATであるASE(日月光半導体製造)も出資先であるDeca Technologiesの技術などをベースに、高雄地区で18年後半からの立ち上げを予定する。

ここ1~2年が勝負

量産および投資案件が着実に増えてきたFOPLPだが、まだまだ技術的課題が多いのも実情だ。力成はFOPLPで2/2umが実現可能とコメントしているが、基本的に露光装置の制約により、FOWLPに比べてファインピッチ対応で不利な面がある。また、樹脂封止技術も充填性の問題を抱え、フィルム材料へのシフトなども念頭に開発がまだまだ途上の段階だ。FOPLPがメジャーな半導体パッケージ技術になれるかどうか、ここ1~2年が勝負といえそうだ。

電子デバイス産業新聞 副編集長 稲葉 雅巳